# Article A Low-Power Analog Integrated Euclidean Distance Radial Basis Function Classifier

Vassilis Alimisis \*, Christos Dimas 匝 and Paul P. Sotiriadis \*

Department of Electrical and Computer Engineering, National Technical University of Athens, 15773 Athens, Greece; chdim@central.ntua.gr

\* Correspondence: alimisisv@gmail.com (V.A.); pps@ieee.org (P.P.S.)

**Abstract:** This study introduces a low-power analog integrated Euclidean distance radial basis function classifier. The high-level architecture is composed of several Manhattan distance circuits in connection with a current comparator circuit. Notably, each implementation was designed with modularity and scalability in mind, effectively accommodating variations in the classification parameters. The proposed classifier's operational principles are meticulously detailed, tailored for low-power, low-voltage, and fully tunable implementations, specifically targeting biomedical applications. This design methodology materialized within a 90 nm CMOS process, utilizing the Cadence IC Suite for the comprehensive management of both the schematic and layout design aspects. During the verification phase, post-layout simulation results were meticulously cross-referenced with software-based classifier implementations. Also, a comparison study with related analog classifiers is provided. Through the simulation results and comparative study, the design architecture's accuracy and sensitivity were effectively validated and confirmed.

Keywords: analog VLSI; low-power design; cardiovascular disease; machine learning; analog classifiers

## 1. Introduction

In the realm of biomedical engineering, the integration of machine learning (ML) stands as a pioneering force reshaping the landscape of healthcare and technological advancements [1]. ML algorithms have emerged as invaluable tools, revolutionizing the analysis of complex biological data, such as genomic sequences, medical images, and physiological signals [2]. Through sophisticated pattern recognition and predictive modeling, these algorithms unveil intricate relationships within biomedical datasets, offering insights that were once elusive [3]. This synergy between machine learning and biomedical engineering not only expedites the discovery of novel treatments and diagnostic tools, but also fosters personalized healthcare approaches, tailoring interventions to individual genetic profiles and disease susceptibilities [4].

The convergence of ML and biomedical engineering creates a new era of precision medicine, transcending traditional medical paradigms [5]. By harnessing vast datasets and employing intricate algorithms, researchers can decipher the underlying mechanisms of diseases, unlocking unprecedented avenues for early detection and intervention [6]. Moreover, these innovations catalyze the development of smart medical devices and systems, facilitating real-time patient monitoring, diagnostics, and therapy optimization [7]. As ML algorithms continue to evolve and adapt, the synergy with biomedical engineering not only augments our understanding of intricate biological systems, but also propels the translation of research findings into tangible solutions that enhance patient care and outcomes [8].

The fusion of wearable devices with ML in biomedical engineering represents a transformative synergy that redefines the landscape of personalized healthcare [9]. These wearable sensors, ranging from smartwatches to biosensing patches, generate a torrent of

Citation: Alimisis, V.; Dimas, C.; Sotiriadis, P.P. A Low-Power Analog Integrated Euclidean Distance Radial Basis Function Classifier. *Electronics* 2024, *13*, 921. https://doi.org/10.3390/ electronics13050921

Academic Editor: Fabian Khateb

Received: 8 January 2024 Revised: 12 February 2024 Accepted: 26 February 2024 Published: 28 February 2024

**Copyright:** © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). real-time physiological data, capturing intricate details of an individual's health status [10]. ML algorithms, adept at deciphering patterns within these vast datasets, enable the extraction of meaningful insights, facilitating early disease detection, continuous monitoring, and personalized interventions [11]. This amalgamation not only empowers individuals to actively engage in their well-being, but also fosters a proactive healthcare approach, where predictive analytics and adaptive algorithms guide tailored interventions, optimizing health outcomes and revolutionizing the paradigm of preventive medicine [12].

Regarding biomedical engineering, the necessity of low-power solutions stands as a pivotal imperative, driving innovation towards more-efficient and -sustainable healthcare technologies [13]. The quest for low-power consumption in biomedical devices is paramount, particularly in wearable sensors, implantable devices, and point-of-care diagnostics [14]. These solutions not only enhance patient comfort and compliance, but also extend device lifespans while minimizing the need for frequent interventions or replacements [15]. Moreover, low-power technologies play a critical role in enabling continuous monitoring, facilitating real-time data acquisition and transmission without imposing excessive energy demands [16]. As the demand for portable, remote monitoring devices surges, low-power solutions not only optimize battery life, but also pave the way for the seamless integration of technology into everyday life, ensuring prolonged and unobtrusive monitoring for improved patient outcomes [17]. The development of such energy-efficient solutions represents a fundamental pillar in advancing biomedical engineering, fostering the creation of scalable, sustainable, and patient-centric healthcare innovations [18].

Emerging computing paradigms, like analog computing, are poised to revolutionize biomedical engineering by offering novel approaches to process and analyze complex biological data, with low power consumption [19–21]. Analog computing, with its ability to handle continuous signals and perform computations closer to the natural world's analog nature, presents a promising frontier in modeling biological systems [19,20]. This paradigm's unique capacity to mimic biological processes, such as neural networks or physiological responses, holds tremendous potential in decoding intricate biological mechanisms and optimizing healthcare solutions [19,20]. By leveraging the inherent parallelism and efficiency of analog computations, biomedical engineers can create innovative platforms capable of rapid and nuanced analysis of biological signals, leading to breakthroughs in diagnostics, personalized treatments, and the development of biologically inspired computing systems tailored to address healthcare challenges with unparalleled precision and efficiency [22].

Motivated by the necessity for low-power smart biosensors [23,24], this study combines sub-threshold analog computing techniques with ML methodologies [25]. The present work introduces a low-power (less than 430 nW), low-voltage (0.6 V), analog integrated Euclidean distance radial basis function (RBF) classifier, tailored for real-world biomedical classification problems [26]. This methodology is grounded upon an RBF mathematical model [27], employing two primary sub-circuits. Core components include an ultra-lowpower Manhattan (approximating Euclidean) distance function circuit [28] and current comparator circuit [29]. Experiments were carried out using a TSMC 90nm CMOS technique, employing the Cadence IC design Suite, and contrasted with a software-oriented execution. Moreover, the efficiency of this design was validated via Monte Carlo assessment, affirming its responsiveness and operational effectiveness.

The remainder of this document is structured as outlined below. Section 2 covers the contextual framework of this research. This encompasses an examination of existing literature and the mathematical model employed. In Section 3, we introduce the outlined high-level configuration of the analog classifier. Moreover, a detailed analysis of the primary components constituting the analog classifier is presented. Section 4 delves into the validation of the proposed architecture using a real-world cardiovascular dataset. Included within this section are comparative evaluations between hardware and software implementations, along with sensitivity assessments. Section 5 comprises a comparative

study and discussion of the findings. Lastly, in Section 6, conclusive remarks summarizing the discoveries and implications of this investigation are provided.

#### 2. Background

## 2.1. Related Literature

The current global landscape is inundated with a diverse range of data formats—text, images, videos, and more—which are projected to continue growing significantly in the future [30,31]. Machine learning (ML) stands as a promising avenue for distilling meaning from this vast pool of data. Being interdisciplinary in nature, ML merges with mathematical domains like statistics, information theory, game theory, and optimization [27,32]. This fusion of methodologies and technologies acts as a conduit for effectively managing this deluge of data. Moreover, automated algorithms possess the capability to uncover meaningful patterns or hypotheses that might evade human perception. While traditionally confined to software execution, there is a rising trend towards adapting these algorithms and models for hardware-friendly implementations [33,34].

Three distinct hardware design methodologies emerge, each with its own merits and limitations. These approaches encompass analog, digital, and mixed-mode implementations. Digital circuits, commonly employed in ML applications, offer advantages in achieving heightened classification accuracy, adaptability, and programmability [35]. However, they pose significant challenges in terms of high power consumption and spatial requirements due to their intensive data transactions and rapid operations. In contrast, specialized analog hardware ML architectures offer cost-effective parallelism through lowpower computation [36]. Yet, accuracy faces challenges due to imprecise circuit parameters caused by noise and limited precision. Furthermore, certain mixed-mode architectures leverage both analog and digital techniques to achieve reduced power consumption and compact footprints [37]. However, these solutions contend with additional costs associated with domain conversion.

Architectures tailored specifically to ML algorithms and models in an analog hardware implementation leverage circuits grounded in Gaussian functions [38]. A subsection consolidates the distinctive features of system-level implementations integrated with Gaussian function circuitry. The proposed ML systems encompass various neural networks such as radial basis function neural networks (RBF NNs) [39–49], offering a comprehensive The related works [41,44,45,48,50] have fabricated and tested the design framework. classifier. Either toy datasets or application-specific implementations have been analyzed. Additionally, these systems include other neural networks like multi-layer perceptron (MLP), the radial basis function network (RBFN) [44,50], the Gaussian RBF NN (GRBF NN) [51,52], the Gaussian mixture model (GMM) [53], Bayes classifiers [54], K-means-based classifiers [55], voting classifiers [56], fuzzy classifiers [57], threshold classifiers [58], and centroid classifiers [59]. Moreover, other algorithms and classifiers like support vector machine (SVM) [60-62], support vector regression (SVR) [63], single-class support vector domain description (SVDD) [64], pattern-matching classifiers [65,66], vector quantizers [67,68], a deep ML (DML) engine [69], a similarity evaluation circuit [70], a long short-term memory (LSTM) [71–74], and a self-organizing map (SOM) [75] are encompassed within this spectrum. Gaussian function circuits form the fundamental basis for executing two crucial functions essential to various ML algorithms: (a) kernel density and (b) distance computation. Most of these applications cater to input dimensions below 65 dimensions, with some instances not specifying an upper limit [40,50,51,67], thus accommodating high-definition image classification.

Based on the above analysis and bibliography, most classifiers presented have been general-purpose. More specifically, they presented a generalized topology and tested it on toy datasets [39–49]. On the other hand, there are application-specific implementations that combine data from real-world datasets related to biomedical engineering, computer vision, image classification, navigation, fuzzy control, sensor fusion, etc. [39–49]. To carry out an on-chip classification process, fundamental key issues such as implementing more

complex features in the analog domain (feature extraction) need to be addressed [76,77]. Other solutions to this include a digital implementation and achieving conversion through low-power current-mode digital-to-analog converters (DACs) [78]. Additionally, reducing power consumption in the analog front-end, which performs the appropriate signal processing, is necessary [79]. Furthermore, the need for low-power non-volatile memories is evident, which will solve the issue of storing data extracted from training [80]. Obviously, the combination of pure analog with memristors or neuromorphic or mixed-signal implementations would be some of the solutions to the existing problems [81]. However, since the ultimate goal is low power consumption, a more-analog IC approach is desirable. Finally, choosing the appropriate algorithm for each dataset is crucial and should have its own weight in the study.

#### 2.2. Mathematical Model

RBFs represent real, positive-valued functions reliant on the distance between an input vector and a fixed point [27,82]. The proximity of the input to the fixed point inversely correlates with the RBF's value. These functions include the Euclidean, Manhattan, and polyharmonic spline, among others. Commonly employed for mathematical approximations, interpolations, serving as activation functions in neural networks (NN), or functioning as kernels in ML algorithms, RBFs hold versatile applications. A multivariate Euclidean RBF is formulated based on the Euclidean norm. The Euclidean distance, also known as the two-norm distance or Euclidean norm, quantifies the direct distance between two points in a Euclidean space. In  $R^n$ , the Euclidean distance between two points, *p* and *q*, is computed using the Euclidean norm as follows:

$$d_c(X) = ||p - q|| = \sqrt{(p_1 - q_1)^2 + (p_2 - q_2)^2 + (p_n - q_n)^2}.$$

(1)

The classifier's output corresponds to the class having the shortest distance from the input vector:

$$y = \underset{c \in \{1, ..., N_{cla}\}}{\operatorname{argmin}} \{ d_c(X) \}.$$

(2)

Based on this distance metric, the overall classifier determines the winning class by applying the argmin operator in this metric.

The implementation presented in the next section is based on an approximation of the aforementioned mathematical model. This specific mathematical model describes the operation of the software-based classifier, which is approached with the proposed architecture. Additionally, the circuit used for distance calculation is also an approximation of the Euclidean norm of the software. The above approaches were made with the aim of low-power operation, that is to have an implementation with the minimum possible power supply and the operation of all transistors in the sub-threshold region (low-voltage and low-current). Furthermore, low power consumption is based on the behavior of the structural element itself (activation circuit), which does not lose its behavior even with small currents. Also, the same implementation could be achieved both using transistors operating in saturation (non power-efficient) and with a structural element that would approximate the Euclidean distance with greater accuracy (more-complex implementation). Finally, the high-level architecture itself could be different using more structural blocks, but it is not certain whether it would increase the accuracy.

#### 3. Proposed Architecture and Main Circuits

Exploring the fundamental concept of the RBF-based classifier takes precedence in this segment. To illuminate the reasoning behind this particular design, envision a scenario: the classification of  $N_{cla}$  separate classes (referred to as class), each with  $N_d$  inputs (features). This adaptability expands to include the accommodation of diverse input dimensions and classes.

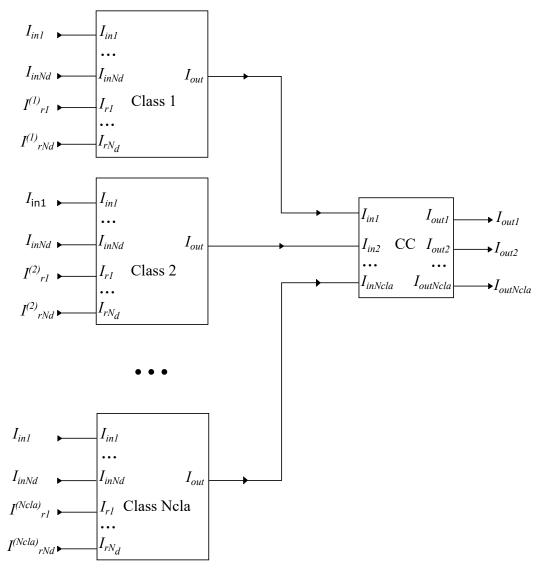

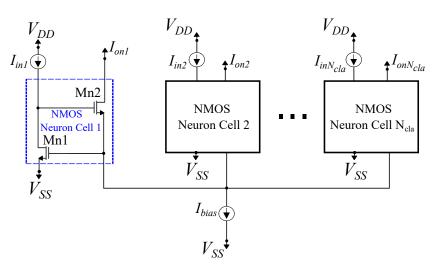

The diagram illustrating the proposed structure for the analog integrated RBF classifier is illustrated in Figure 1. Following the formulation of the classification problem outlined previously, the classifier is composed of a singular current comparator (CC) block encompassing  $N_{cla}$  inputs and an equivalent number of classes. Each of these classes comprises  $N_d$  sub-cells, delineating  $N_d$  features. These sub-cells operate as circuits embodying the Manhattan distance (as the approximation of the Euclidean one), receiving  $N_d$  inputs. Their function involves computing the distance of an input vector **X** associated with a particular class by utilizing the Manhattan distance for each feature, as described in the mathematical model.

**Figure 1.** Analog integrated RBF-based classifier with  $N_{cla}$  classes and  $N_d$  features. This is a conceptual design describing the proposed architecture.

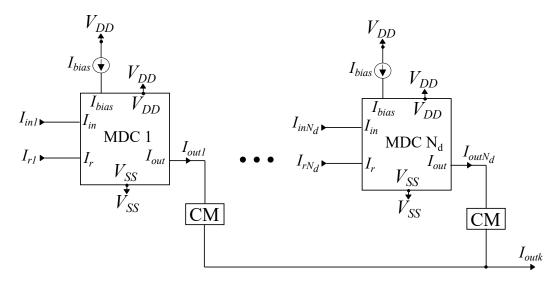

Also, section analysis thoroughly examines the primary building circuits crucial for implementing the RBF-based classifier. Each classifier necessitates two key blocks: the class and a CC. Additionally, every cell demands two primary components: the Manhattan distance circuit (MDC) and cascode current mirrors (CMs). To uphold precision and reduce potential distortions, this summation process within a class is achieved by employing CMs, as shown in Figure 2. The dimensions of the transistors within each cascode current mirror are  $\frac{W}{L} = \frac{3.2 \ \mu m}{1.6 \ \mu m}$ . These class cells essentially function as multidimensional distance circuitry with  $N_d$  inputs. Employing  $N_d$  MDCs, as depicted in Figure 2, results in the collective output simulating an  $N_d$ -dimensional Manhattan distance function. The indi-

vidual parameters ( $I_r$ ) for each MDC are independently adjusted. The foundation of the architectural design methodology lies in the prioritization of employing ultra-low-power circuits as fundamental elements in constructing the core cells. As a result, all transistors within the architecture function within the sub-threshold range. The classification outcome remains unaffected by the inherent current noise in the utilized circuits, as its worst-case value, determined post-simulations, remained below 20 pA—well within the operational frequency range (less than 1 kHz). Given its low-power implementation, the power supply voltages were configured as  $V_{DD} = -V_{SS} = 0.3$  V, while  $I_r$  ranged between 3 and 12 nA.

**Figure 2.** Analog integrated implementation of a class with  $N_d$  features. Extra CMs are employed in order to deal with potential distortions.

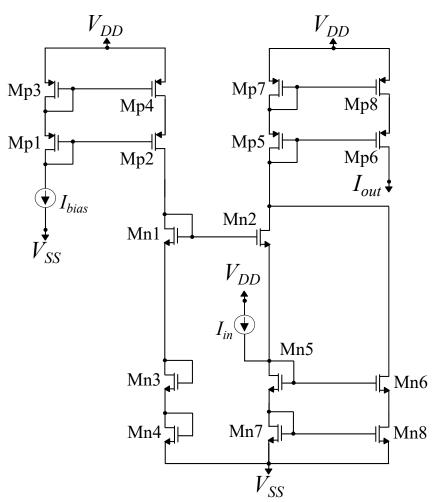

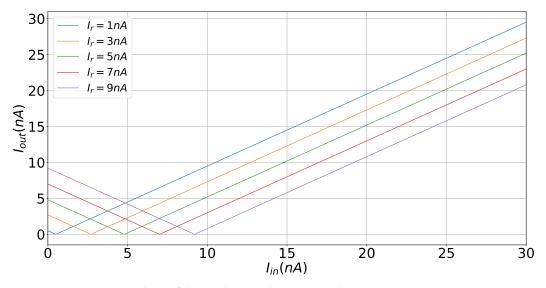

To implement the Manhattan distance function as defined in the mathematical model, we utilized a current-mode MDC [28], illustrated in Figure 3. Operating in a translinear manner, this circuit approximates the mathematical expression:  $||I_{in} - I_r||$ . The summation process within the current domain is straightforward, accomplished by connecting wires containing the currents. Moreover, to optimize the mirroring performance, even with low bias currents, cascode CMs have been integrated. The behavior of the circuit was verified through the simulation results in Figure 4. Information regarding the dimensions of the transistors can be found in Table 1.

Table 1. MDC transistors' dimensions.

| NMOS             | W/L (µm/µm) | PMOS              | W/L (μm/μm) |

|------------------|-------------|-------------------|-------------|

| $M_{n1}, M_{n2}$ | 2.8/0.4     | $M_{p1} - M_{p4}$ | 1.6/1.6     |

| $M_{n3}, M_{n4}$ | 1.6/1.6     | $M_{p5}, M_{p6}$  | 1.6/1.6     |

| $M_{n5}-M_{n8}$  | 3.2/1.6     | $M_{p7}, M_{p8}$  | 2.4/1.6     |

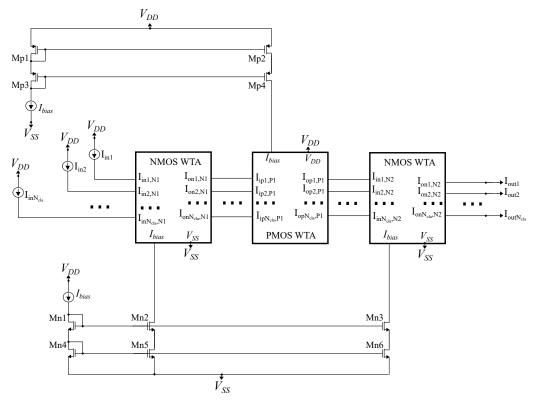

The next circuit under consideration is the CC. Since, in this work, a 2-class classification problem is analyzed, a cascaded winner-takes-all (WTA) circuit was employed. This circuit is used as an argmax operator. In this work, since we need the smallest distance, the winner is described by the minimum output current (for a two-class problem). For a generic illustration, an argmin operator is necessary.

The analysis focuses on the behavior of a cascaded winner-takes-all (WTA) mechanism. To understand the modified WTA circuit employed in this study, a concise examination of the conventional Lazzaro WTA circuit is referenced [29]. The Lazzaro WTA circuit setup involves  $N_{cla}$  neurons interconnected, sharing a common  $I_{bias}$  current, as depicted in Figure 5. Each neuron represents a distinct class and independently manages its input and output functions. Among these neurons, the one receiving the highest input current gener-

ates a non-zero output equal to  $I_{bias}$ , while the rest produce an output of zero. Scenarios with similar input currents may result in multiple winners, a situation often considered undesirable in most classification contexts.

**Figure 3.** MDC for the realization of the Manhattan distance.  $I_{out}$  is the output of the circuit, which has the lowest value for  $I_{in} = I_r$ .

Figure 4. Parametric analysis of the implemented MDC over the circuit's parameters.

Figure 5. A N<sub>cla</sub>-neuron standard Lazzaro NMOS winner-takes-all (WTA) circuit.

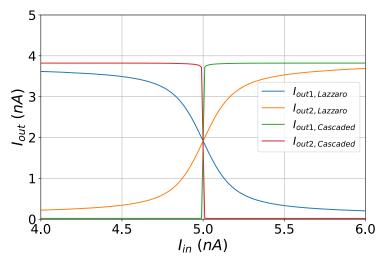

One approach to tackle this challenge involves implementing a cascaded WTA circuit, illustrated in Figure 6. This devised setup integrates three WTA circuits interconnected in a cascaded manner [83]. Figure 7 provides visual representations of the one-dimensional decision boundaries for both the traditional Lazzaro WTA circuit and the proposed cascaded version. Notably, the cascaded WTA circuit exhibits considerably sharper decision boundaries compared to the basic Lazzaro WTA circuit. As a result, the cascaded topology emerges as the more-suitable choice for the critical argmax operation of the classifier (though argmin might be more appropriate for a generic classifier). The transistor dimensions for both the NMOS and PMOS neurons in Figure 6 were configured at  $W/L = 0.4 \,\mu\text{m}/1.6 \,\mu\text{m}$ . The preference for elongated transistors was driven by the necessity for reduced noise and enhanced linearity, which are pivotal for the effective execution of the argmax operator.

**Figure 6.** A cascaded NMOS–PMOS–NMOS WTA circuit. It is utilized to improve the performance of the standard WTA circuit.

Figure 7. Decision boundaries of the standard and the cascaded WTA circuit.

### 4. Application Example and Simulation Results

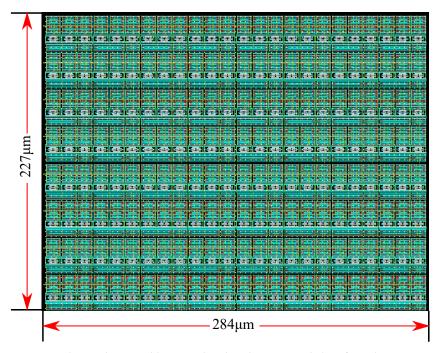

In this segment, the performance of the proposed classifier is evaluated using realworld data related to cardiovascular disease prediction [26] to validate its functionality. The classifier was developed utilizing the Cadence IC suite within a TSMC 90 nm CMOS process. All simulation outcomes were based on the layout (post-layout simulations), represented in Figure 8. This consists of  $N_{cla} = 2$  classes and  $N_d = 11$  features. The Cardiovascular Disease Dataset available on Kaggle presents a comprehensive collection of health-related data associated with individuals susceptible to cardiovascular issues. This dataset encompasses a range of attributes that are vital in predicting the likelihood of cardiovascular disease in patients. It comprises both numerical and categorical features, including age, gender, height, weight, blood pressure measurements, cholesterol levels, glucose levels, and various lifestyle indicators like smoking habits and physical activity. Each entry in this dataset is linked to a binary classification label indicating the presence or absence of cardiovascular disease.

**Figure 8.** The implemented layout related to the proposed classifier. The common centroid technique is used in order to minimize random effects over PVT variations.

Notably, this dataset provides a rich resource for exploratory data analysis and predictive modeling. It holds records for a considerable number of patients, allowing for robust statistical analysis and ML model training. The dataset's diversity in features provides a comprehensive scope for feature engineering, model validation, and evaluation, making it an invaluable asset for researchers, data scientists, and healthcare professionals aiming to develop predictive models or derive meaningful insights regarding cardiovascular health and associated risk factors.

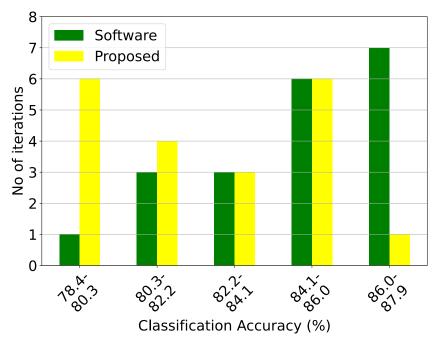

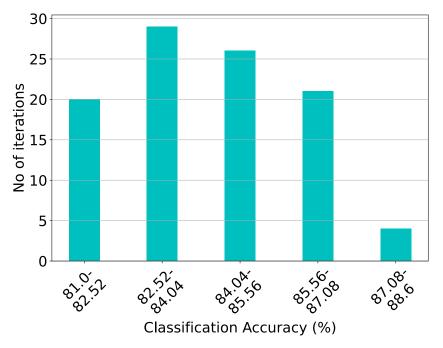

Based on the proposed design methodology and the simulation results of the software implementation, the generic RBF-based classifier consists of  $N_{Cla} = 2$  classes and  $N_d = 11$  input dimensions. The high-level architecture of this classifier is illustrated in Figure 1. Specifically, each class comprises two 11-D MDCs, representing the clusters, along with the current mirrors utilized to aggregate the output currents of each cluster (considering we have only one cluster per class). Figure 9 showcases the classification accuracy for both the proposed hardware and software implementations, covering a total of 20 distinct training test cases for the relevant dataset. These results are also summarized in Table 2. Regarding sensitivity analysis, the Monte Carlo histogram displayed in Figure 10, comprising 100 runs, exhibits a mean value of  $\mu_M = 84.25\%$  and a standard deviation of  $\sigma_M = 1.23\%$ .

**Figure 9.** Classification results of the proposed architecture and the equivalent software model on the related dataset over 20 iterations.

Table 2. Proposed architecture's accuracy for the related dataset (over 20 iterations).

| Method   | Best   | Worst  | Mean   | <b>Variance</b><br>1.87% |  |

|----------|--------|--------|--------|--------------------------|--|

| Software | 87.90% | 79.80% | 85.10% |                          |  |

| Hardware | 86.60% | 78.40% | 82.50% | 1.93%                    |  |

Based on the post-layout results presented, both the individual building blocks and the high-level architecture exhibited the desired behavior. The MDC approached the Mahalanobis distance almost entirely, with slight deviations attributed to mismatches in the mirrors and the early effect phenomenon. It is noteworthy that, for  $I_{in} = I_r$ , the circuit produced the minimum output, which is the desired outcome. Regarding the high-level architecture, the post-layout results demonstrated robust behavior as there was minimal deviation compared to the software accuracy and a slight variance in the Monte Carlo analysis. Furthermore, the nature of the WTA provides a significant advantage even if the currents have small deviations from the theoretical value. Specifically, high or low values will occur at the respective outputs, depending on the difference in the current values, rather than the exact value.

**Figure 10.** Post-layout Monte Carlo simulation results of the proposed architecture on the related dataset with  $\mu_M = 84.25\%$  and  $\sigma_M = 1.23\%$  (for 1 of the previous 20 iterations).

# 5. Comparison and Discussion

The literature highlights a trend where analog classifiers are predominantly customized for specific applications. Comparing various ML models or hardware implementations on a unified application to derive equitable results poses a significant challenge. However, this challenge presents an opportunity to tailor analog classifiers for a shared application, streamlining performance evaluation encompassing both ML models and alternative methods. Table 3 provides an overview of the performance comparisons across various related classifiers. In the context of cardiovascular classification, the Bayes [36], GMM [36], RBF [36,39], LSTM [71], K-means [55], Bayesian [36], RBF neural network (NN) [41], fuzzy [57], SVM [36,42], threshold [36], MLP [50], SVR [63], and centroidbased [36] classifiers are summarized.

This research proposes a solution that strikes a balance between accuracy, power efficiency, and energy consumption per classification when compared to similar classifiers in the domain. In this particular application, handling high input dimensionality is crucial. The suggested configuration holds a significant advantage by eliminating the need for principal component analysis (PCA), allowing the incorporation of all 11 input dimensions without losing vital information. Moreover, it manages more than 20 features without necessitating PCA, unlike cascaded implementations. In contrast, many alternative structures must reduce the dimensions to 16 or fewer (for more-complex problems) to attain optimal accuracy, a significant limitation in previous similar studies [36,41,42,57,63]. While the proposed classifier exhibits proficiency in accurately classifying a wider range of classes, a binary classification scenario was chosen for a fair comparison with binary analog classifiers [36,57].

Regarding classification accuracy, the proposed architecture surpassed most of its counterparts, except MLP [50], LSTM [71], and K-means [55]. Despite achieving higher accuracy, these models entail increased complexity, power consumption, and a larger silicon area due to component numbers. Conversely, the threshold classifier recorded the lowest power consumption among the other classifiers, albeit sacrificing accuracy and

processing speed due to its simplistic model design [36]. In biomedical applications of this nature, swift processing speed is not crucial due to their infrequent occurrence. Hence, in this approach, processing speed is traded for heightened accuracy and optimized power consumption. Additionally, it boasts lower energy consumption per classification compared to all other classifiers.

As shown in Table 3, the proposed implementation achieved the lowest consumption. This confirms the aim of this particular study. More specifically, through the use of the sub-threshold operating region, a significant reduction in consumption was achieved. Additionally, the ability of the circuit itself to operate at very low currents and voltages provides further power efficiency opportunities. Furthermore, through the proposed architecture, there is additional potential for using the minimum possible operating currents. Unlike cascaded implementations (related works), this specific implementation can utilize the full operating range of the circuit, operate at the minimum possible current, and handle a large number of features as there is no current attenuation. Regarding the accuracy of the results, it is primarily related to the approximation of the software model by the hardware. This means that, if the model is too simple and the approximation is not optimal, the accuracy will be low.

Table 3. Analog classifiers' comparison on the cardiovascular prediction dataset.

| Classifier         | Best   | Worst  | Mean   | Power Consumption | Processing Speed                                             | Energy per Classification                      |

|--------------------|--------|--------|--------|-------------------|--------------------------------------------------------------|------------------------------------------------|

| This work          | 86.60% | 78.40% | 82.50% | 430 nW            | 270 K classifications<br>s                                   | 1.59 pJ<br>classification                      |

| GMM [36]           | 85.20% | 76.10% | 81.12% | 1745 nW           | $112 \text{ K} \frac{\text{classifications}}{\text{s}}$      | 15.6 pJ<br>classification                      |

| RBF [36]           | 84.30% | 73.40% | 80.77% | 1940 nW           | $100 \text{ K} \frac{\text{classifications}}{\text{s}}$      | 19.4 pJ<br>classification                      |

| Bayes [36]         | 84.70% | 75.40% | 81.07% | 984 nW            | $130 \text{ K} \frac{\text{classifications}}{\text{s}}$      | 7.6 pJ<br>classification                       |

| Threshold [36]     | 81.20% | 72.40% | 79.31% | 734 nW            | 130 K classifications<br>s                                   | 5.65 pJ<br>classification                      |

| Centroid [36]      | 82.50% | 77.30% | 81.43% | 1020 nW           | $112 \text{ K} \frac{\text{classifications}}{\text{s}}$      | 9.1 pJ<br>classification                       |

| SVM [36]           | 87.80% | 79.60% | 83.43% | 9.73 μW           | $140 \text{ K} \frac{\text{classifications}}{\text{s}}$      | 69.5 pJ<br>classification                      |

| RBF [39]           | 85.90  | 79.90  | 82.55  | 15.61 μW          | $170 \text{ K} \frac{\text{classifications}}{\text{s}}$      | 91.82 pJ<br>classification                     |

| <b>RBF NN [41]</b> | 79.30  | 72.50  | 77.51  | 1293 nW           | $270 \text{ K} \frac{\text{classifications}}{\text{s}}$      | $\frac{4.8 \text{ pJ}}{\text{classification}}$ |

| SVM [42]           | 82.70  | 79.10  | 81.98  | 281.3 μW          | 870 K classifications                                        | 323.3 pJ<br>classification                     |

| MLP [50]           | 91.30  | 88.20  | 89.52  | 932.43 μW         | 930 K <u>classifications</u><br>s                            | $\frac{1.0 \text{ nJ}}{\text{classification}}$ |

| K-means [55]       | 92.70  | 86.40  | 91.27  | 340.28 μW         | $5 M \frac{\text{classifications}}{s}$                       | 68.1 pJ<br>classification                      |

| Fuzzy [57]         | 87.10  | 79.30  | 84.41  | 972 nW            | $4.55 \mathrm{K} rac{\mathrm{classifications}}{\mathrm{s}}$ | 213.6 pJ<br>classification                     |

| SVR [63]           | 91.40  | 86.70  | 88.67  | 123.76 μW         | 870 K classifications                                        | 142.26 pJ<br>classification                    |

| LSTM [71]          | 100.00 | 97.20  | 99.43  | 39.77 mW          | $870 \text{ M} rac{\text{classifications}}{\text{s}}$       | 45.7 pJ<br>classification                      |

## 6. Conclusions

This research pioneers a new methodology in an adjustable analog integrated Euclidean (Manhattan) distance RBF classifier. By strategically manipulating MDC and WTA circuits, the study showcases the ability to create RBF-based classifiers tailored to a wide array of scenarios, accommodating varied class quantities, cluster setups, and data dimensions. To demonstrate the adaptability and efficiency of this approach, the study applies the proposed design methodology to analyze a distinct real-world dataset curated specifically for diagnosing cardiovascular disease. Comprehensive evaluations and comparisons of classification outcomes within these scenarios emphasize the efficiency of the proposed methodology and validate the adjustments made. This innovative design approach holds promise as a fundamental tool for crafting more-sophisticated and -precise diagnostic sys-

tems, offering potential applications across diverse domains where flexible and adjustable classifiers are pivotal for accurate analyses and predictions.

**Author Contributions:** Investigation, V.A.; writing—original draft, V.A. and C.D.; writing—review and editing, V.A., C.D. and P.P.S. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

**Data Availability Statement:** The data used in this study are openly available in the Cardiovascular Disease Dataset at https://www.kaggle.com/datasets/sulianova/cardiovascular-disease-dataset (accessed on 20 December 2023) reference number [26].

Conflicts of Interest: The authors declare no conflicts of interest.

#### References

- 1. Datta, S.P.A. Future Healthcare: Bioinformatics, Nano-Sensors, and Emerging Innovations; CRC Press: Boca Raton, FL, USA, 2016; Volume 247.

- 2. Ahmed, Z.; Mohamed, K.; Zeeshan, S.; Dong, X. Artificial intelligence with multi-functional machine learning platform development for better healthcare and precision medicine. *Database* **2020**, *2020*, baaa010. [CrossRef] [PubMed]

- 3. Bzdok, D.; Ioannidis, J.P. Exploration, inference, and prediction in neuroscience and biomedicine. *Trends Neurosci.* **2019**, 42, 251–262. [CrossRef] [PubMed]

- 4. Biswas, A.; Kumari, A.; Gaikwad, D.; Pandey, D.K. Revolutionizing Biological Science: The Synergy of Genomics in Health, Bioinformatics, Agriculture, and Artificial Intelligence. *OMICS A J. Integr. Biol.* **2023**, 27, 550–569. [CrossRef] [PubMed]

- Jeyaraman, M.; Ratna, H.V.K.; Jeyaraman, N.; Venkatesan, A.; Ramasubramanian, S.; Yadav, S.; Ratna, H.V. Leveraging Artificial Intelligence and Machine Learning in Regenerative Orthopedics: A Paradigm Shift in Patient Care. *Cureus* 2023, 15, e49756. [CrossRef] [PubMed]

- Kunduru, A.R. Machine Learning in Drug Discovery: A Comprehensive Analysis of Applications, Challenges, and Future Directions. Int. J. Orange Technol. 2023, 5, 29–37.

- 7. Navaz, A.N.; Serhani, M.A.; El Kassabi, H.T.; Al-Qirim, N.; Ismail, H. Trends, technologies, and key challenges in smart and connected healthcare. *IEEE Access* 2021, *9*, 74044–74067. [CrossRef] [PubMed]

- Saceleanu, V.M.; Toader, C.; Ples, H.; Covache-Busuioc, R.A.; Costin, H.P.; Bratu, B.G.; Dumitrascu, D.I.; Bordeianu, A.; Corlatescu, A.D.; Ciurea, A.V. Integrative approaches in acute ischemic stroke: From symptom recognition to future innovations. *Biomedicines* 2023, 11, 2617. [CrossRef] [PubMed]

- 9. Zheng, L.; Cao, M.; Du, Y.; Liu, Q.; Emran, M.Y.; Yousef, A.K.; Sun, M.; Ma, C.; Zhou, M. Artificial enzyme innovations in electrochemical devices: Advancing wearable and portable sensing technologies. *Nanoscale* **2023**, *16*, 44–60. [CrossRef]

- Mandal, D.; Bag, S. Smart Health Monitoring Using Wearable Device Sensors: A Brief Review. Int. J. Pharm. Sci. 2023, 14, 46–61. [CrossRef]

- 11. Rasool, S.; Husnain, A.; Saeed, A.; Gill, A.Y.; Hussain, H.K. Harnessing Predictive Power: Exploring the Crucial Role of Machine Learning in Early Disease Detection. *JURIHUM J. Inov. Dan Hum.* **2023**, *1*, 302–315.

- 12. Gaur, L.; Jhanjhi, N.Z. Metaverse Applications for Intelligent Healthcare; IGI Global: Hershey, PA, USA, 2023.

- 13. Gupta, R.; Biswas, D. Health Monitoring Systems: An Enabling Technology for Patient Care; CRC Press: Boca Raton, FL, USA, 2019.

- 14. Dahiya, A.S.; Thireau, J.; Boudaden, J.; Lal, S.; Gulzar, U.; Zhang, Y.; Gil, T.; Azemard, N.; Ramm, P.; Kiessling, T.; et al. Energy autonomous wearable sensors for smart healthcare: A review. *J. Electrochem. Soc.* **2019**, *167*, 037516. [CrossRef]

- 15. Heng, W.; Solomon, S.; Gao, W. Flexible electronics and devices as human–machine interfaces for medical robotics. *Adv. Mater.* **2022**, *34*, 2107902. [CrossRef] [PubMed]

- 16. Ma, D.; Lan, G.; Hassan, M.; Hu, W.; Das, S.K. Sensing, computing, and communications for energy harvesting IoTs: A survey. *IEEE Commun. Surv. Tutor.* **2019**, *22*, 1222–1250. [CrossRef]

- 17. Folea, S.C.; Mois, G. A low-power wireless sensor for online ambient monitoring. IEEE Sens. J. 2014, 15, 742–749. [CrossRef]

- 18. Mishra, P.; Singh, G. Internet of medical things healthcare for sustainable smart cities: Current status and future prospects. *Appl. Sci.* **2023**, *13*, 8869. [CrossRef]

- 19. MacLennan, B.J. A Review of Analog Computing; Technical Report UT-CS-07-601 (September); Department of Electrical Engineering & Computer Science, University of Tennessee: Knoxville, TN, USA, 2007.

- 20. Haensch, W.; Gokmen, T.; Puri, R. The next generation of deep learning hardware: Analog computing. *Proc. IEEE* 2018, 107, 108–122. [CrossRef]

- Zhang, Y.; Mirchandani, N.; Onabajo, M.; Shrivastava, A. RSSI amplifier design for a feature extraction technique to detect seizures with analog computing. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 1–5.

- 22. Harun-Ur-Rashid, M.; Jahan, I.; Foyez, T.; Imran, A.B. Bio-Inspired Nanomaterials for Micro/Nanodevices: A New Era in Biomedical Applications. *Micromachines* 2023, 14, 1786. [CrossRef]

- 23. Banerjee, A.; Maity, S.; Mastrangelo, C.H. Nanostructures for biosensing, with a brief overview on cancer detection, IoT, and the role of machine learning in smart biosensors. *Sensors* **2021**, *21*, 1253. [CrossRef]

- Sharma, A.; Polley, A.; Lee, S.B.; Narayanan, S.; Li, W.; Sculley, T.; Ramaswamy, S. A Sub-60 μA Multimodal Smart Biosensing SoC with >80-dB SNR, 35-μA Photoplethysmography Signal Chain. *IEEE J. Solid State Circuits* 2017, 52, 1021–1033. [CrossRef]

- 25. Wang, A.; Calhoun, B.H.; Chandrakasan, A.P. *Sub-Threshold Design for Ultra Low-Power Systems*; Springer: Berlin/Heidelberg, Germany, 2006; Volume 95.

- Cardiovascular Disease Dataset. Available online: https://www.kaggle.com/datasets/sulianova/cardiovascular-disease-dataset (accessed on 20 December 2023).

- 27. Bishop, C.M.; Nasrabadi, N.M. Pattern Recognition and Machine Learning; Springer: Berlin/Heidelberg, Germany, 2006; Volume 4.

- 28. Gilbert, B. Translinear circuits: An historical overview. *Analog Integr. Circuits Signal Process.* **1996**, *9*, 95–118. [CrossRef]

- Lazzaro, J.; Ryckebusch, S.; Mahowald, M.A.; Mead, C.A. Winner-take-all networks of O(N) complexity. *Adv. Neural Inf. Process.* Syst. 1988, 1, 703–711.

- 30. Chi, P.; Li, S.; Xu, C.; Zhang, T.; Zhao, J.; Liu, Y.; Wang, Y.; Xie, Y. Prime: A novel processing-in-memory architecture for neural network computation in reram-based main memory. *ACM SIGARCH Comput. Archit. News* **2016**, *44*, 27–39. [CrossRef]

- Shawahna, A.; Sait, S.M.; El-Maleh, A. FPGA-based accelerators of deep learning networks for learning and classification: A review. *IEEE Access* 2018, 7, 7823–7859. [CrossRef]

- 32. Mohri, M.; Rostamizadeh, A.; Talwalkar, A. Foundations of Machine Learning; MIT Press: Cambridge, MA, USA, 2018.

- Liu, S.C.; Kramer, J.; Indiveri, G.; Delbrück, T.; Douglas, R. Analog VLSI: Circuits and Principles; MIT Press: Cambridge, MA, USA, 2002.

Jabri, M.; Coggins, R.J.; Flower, B.G. Adaptive Analog VLSI Neural Systems; Springer Science & Business Media: Berlin/Heidelberg, Germany, 1996.

- 35. Liu, X.; Ounifi, H.A.; Gherbi, A.; Li, W.; Cheriet, M. A hybrid GPU-FPGA based design methodology for enhancing machine learning applications performance. *J. Ambient Intell. Humaniz. Comput.* **2020**, *11*, 2309–2323. [CrossRef]

- 36. Alimisis, V.; Eleftheriou, N.P.; Kamperi, A.; Gennis, G.; Dimas, C.; Sotiriadis, P.P. General Methodology for the Design of Bell-Shaped Analog-Hardware Classifiers. *Electronics* **2023**, *12*, 4211. [CrossRef]

- 37. Fayazi, M.; Colter, Z.; Afshari, E.; Dreslinski, R. Applications of artificial intelligence on the modeling and optimization for analog and mixed-signal circuits: A review. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2021**, *68*, 2418–2431. [CrossRef]

- 38. Alimisis, V.; Gourdouparis, M.; Gennis, G.; Dimas, C.; Sotiriadis, P.P. Analog gaussian function circuit: Architectures, operating principles and applications. *Electronics* **2021**, *10*, 2530. [CrossRef]

- Peng, S.Y.; Hasler, P.E.; Anderson, D.V. An analog programmable multidimensional radial basis function based classifier. *IEEE Trans. Circuits Syst. I Regul. Pap.* 2007, 54, 2148–2158. [CrossRef]

- Dorzhigulov, A.; James, A.P. Generalized bell-shaped membership function generation circuit for memristive neural networks. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 1–5.

- 41. Mohamed, A.R.; Qi, L.; Li, Y.; Wang, G. A generic nano-watt power fully tunable 1-d gaussian kernel circuit for artificial neural network. *IEEE Trans. Circuits Syst. II Express Briefs* 2020, *67*, 1529–1533. [CrossRef]

- Kang, K.; Shibata, T. An on-chip-trainable Gaussian-kernel analog support vector machine. *IEEE Trans. Circuits Syst. I Regul. Pap.* 2009, 57, 1513–1524. [CrossRef]

- Lee, K.; Park, J.; Kim, G.; Hong, I.; Yoo, H.J. A multi-modal and tunable Radial-Basis-Function circuit with supply and temperature compensation. In Proceedings of the 2013 IEEE International Symposium on Circuits and Systems (ISCAS), Beijing, China, 19–23 May 2013; IEEE: Piscataway, NJ, USA, 2013; pp. 1608–1611.

- Watkins, S.S.; Chau, P.M.; Tawel, R. A radial basis function neurocomputer implemented with analog VLSI circuits. In Proceedings of the [Proceedings 1992] IJCNN International Joint Conference on Neural Networks, Baltimore, MD, USA, 7–11 June 1992; IEEE: Piscataway, NJ, USA, 1992; Volume 2, pp. 607–612.

- 45. Verleysen, M.; Thissen, P.; Voz, J.L.; Madrenas, J. An analog processor architecture for a neural network classifier. *IEEE Micro* **1994**, 14, 16–28. [CrossRef]

- De Oliveira, J.; Oki, N. An analog implementation of radial basis neural networks (RBNN) using BiCMOS technology. In Proceedings of the 44th IEEE 2001 Midwest Symposium on Circuits and Systems, MWSCAS 2001 (Cat. No. 01CH37257), Dayton, OH, USA, 14–17 August 2001; IEEE: Piscataway, NJ, USA, 2001; Volume 2, pp. 705–708.

- Collins, S.; Marshall, G.F.; Brown, D. An analogue Radial Basis Function circuit using a compact Euclidean Distance calculator. In Proceedings of the IEEE International Symposium on Circuits and Systems-ISCAS'94, London, UK, 30 May–2 June 1994; IEEE: Piscataway, NJ, USA, 1994; Volume 6, pp. 233–236.

- 48. Anderson, J.; Platt, J.; Kirk, D.B. An analog VLSI chip for radial basis functions. Adv. Neural Inf. Process. Syst. 1992, 5.

- Hsieh, Y.T.; Anjum, K.; Pompili, D. Ultra-low Power Analog Recurrent Neural Network Design Approximation for Wireless Health Monitoring. In Proceedings of the 2022 IEEE 19th International Conference on Mobile Ad Hoc and Smart Systems (MASS), Denver, CO, USA, 19–23 October 2022; pp. 211–219. [CrossRef]

- 50. Lee, K.; Park, J.; Yoo, H.J. A low-power, mixed-mode neural network classifier for robust scene classification. *J. Semicond. Technol. Sci.* **2019**, *19*, 129–136. [CrossRef]

- Cevikhas, I.; Ogrenci, A.; Dundar, G.; Balkur, S. VLSI implementation of GRBF (Gaussian radial basis function) networks. In Proceedings of the 2000 IEEE International Symposium on Circuits and Systems (ISCAS), Geneva, Switzerland, 28–31 May 2000; IEEE: Piscataway, NJ, USA, 2000; Volume 3, pp. 646–649.

- 52. Alimisis, V.; Gennis, G.; Dimas, C.; Gourdouparis, M.; Sotiriadis, P.P. An ultra low power analog integrated radial basis function classifier for smart IoT systems. *Analog Integr. Circuits Signal Process.* **2022**, *112*, 225–236. [CrossRef]

- Alimisis, V.; Gennis, G.; Touloupas, K.; Dimas, C.; Gourdouparis, M.; Sotiriadis, P.P. Gaussian Mixture Model classifier analog integrated low-power implementation with applications in fault management detection. *Microelectron. J.* 2022, 126, 105510. [CrossRef]

- Alimisis, V.; Gennis, G.; Dimas, C.; Sotiriadis, P.P. An analog Bayesian classifier implementation, for thyroid disease detection, based on a low-power, current-mode gaussian function circuit. In Proceedings of the 2021 International Conference on Microelectronics (ICM), New Cairo City, Egypt, 19–22 December 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 153–156.

- 55. Zhang, R.; Shibata, T. An analog on-line-learning K-means processor employing fully parallel self-converging circuitry. *Analog Integr. Circuits Signal Process.* 2013, 75, 267–277. [CrossRef]

- 56. Alimisis, V.; Mouzakis, V.; Gennis, G.; Tsouvalas, E.; Dimas, C.; Sotiriadis, P.P. A Hand Gesture Recognition Circuit Utilizing an Analog Voting Classifier. *Electronics* **2022**, *11*, 3915. [CrossRef]

- 57. Georgakilas, E.; Alimisis, V.; Gennis, G.; Aletraris, C.; Dimas, C.; Sotiriadis, P.P. An ultra-low power fully-programmable analog general purpose type-2 fuzzy inference system. *AEU Int. J. Electron. Commun.* **2023**, *170*, 154824. [CrossRef]

- Alimisis, V.; Gennis, G.; Tsouvalas, E.; Dimas, C.; Sotiriadis, P.P. An Analog, Low-Power Threshold Classifier tested on a Bank Note Authentication Dataset. In Proceedings of the 2022 International Conference on Microelectronics (ICM), Casablanca, Morocco, 4–7 December 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 66–69.

- Alimisis, V.; Mouzakis, V.; Gennis, G.; Tsouvalas, E.; Sotiriadis, P.P. An Analog Nearest Class with Multiple Centroids Classifier Implementation, for Depth of Anesthesia Monitoring. In Proceedings of the 2022 International Conference on Smart Systems and Power Management (IC2SPM), Beirut, Lebanon, 10–12 November 2022; IEEE: Piscataway, NJ, USA, 2022; pp. 176–181.

- Peng, S.Y.; Minch, B.A.; Hasler, P. Analog VLSI implementation of support vector machine learning and classification. In Proceedings of the 2008 IEEE International Symposium on Circuits and Systems (ISCAS), Seattle, WA, USA, 18–21 May 2008; IEEE: Piscataway, NJ, USA, 2008; pp. 860–863.

- 61. Zhang, R.; Shibata, T. Fully parallel self-learning analog support vector machine employing compact gaussian generation circuits. *Jpn. J. Appl. Phys.* **2012**, *51*, 04DE10. [CrossRef]

- Alimisis, V.; Gennis, G.; Gourdouparis, M.; Dimas, C.; Sotiriadis, P.P. A Low-Power Analog Integrated Implementation of the Support Vector Machine Algorithm with On-Chip Learning Tested on a Bearing Fault Application. *Sensors* 2023, 23, 3978. [CrossRef]

- 63. Zhang, R.; Uetake, N.; Nakada, T.; Nakashima, Y. Design of programmable analog calculation unit by implementing support vector regression for approximate computing. *IEEE Micro* **2018**, *38*, 73–82. [CrossRef]

- 64. Zhang, R.; Shibata, T. A vlsi hardware implementation study of svdd algorithm using analog gaussian-cell array for on-chip learning. In Proceedings of the 2012 13th International Workshop on Cellular Nanoscale Networks and their Applications, Turin, Italy, 29–31 August 2012; IEEE: Piscataway, NJ, USA, 2012; pp. 1–6.

- 65. Yamasaki, T.; Shibata, T. Analog soft-pattern-matching classifier using floating-gate MOS technology. *IEEE Trans. Neural Netw.* **2003**, *14*, 1257–1265. [CrossRef] [PubMed]

- Yamasaki, T.; Yamamoto, K.; Shibata, T. Analog pattern classifier with flexible matching circuitry based on principal-axisprojection vector representation. In Proceedings of the 27th European Solid-State Circuits Conference, Villach, Austria, 18–20 September 2001; IEEE: Piscataway, NJ, USA, 2001; pp. 197–200.

- Hasler, P.; Smith, P.; Duffy, C.; Gordon, C.; Dugger, J.; Anderson, D. A floating-gate vector-quantizer. In Proceedings of the 2002 45th Midwest Symposium on Circuits and Systems, MWSCAS-2002, Tulsa, OK, USA, 4–7 August 2002; IEEE: Piscataway, NJ, USA, 2002; Volume 1, pp. 1–196.

- 68. Cauwenberghs, G.; Pedroni, V. A charge-based CMOS parallel analog vector quantizer. Adv. Neural Inf. Process. Syst. 1994, 7.

- 69. Lu, J.; Young, S.; Arel, I.; Holleman, J. A 1 tops/w analog deep machine-learning engine with floating-gate storage in 0.13 μm cmos. *IEEE J. Solid-State Circuits* **2014**, *50*, 270–281. [CrossRef]

- Yamasaki, T.; Shibata, T. An analog similarity evaluation circuit featuring variable functional forms. In Proceedings of the ISCAS 2001. The 2001 IEEE International Symposium on Circuits and Systems (Cat. No. 01CH37196), Sydney, NSW, Australia, 6–9 May 2001; IEEE: Piscataway, NJ, USA, 2001; Volume 3, pp. 561–564.

- 71. Zhao, Z.; Srivastava, A.; Peng, L.; Chen, Q. Long short-term memory network design for analog computing. *ACM J. Emerg. Technol. Comput. Syst. (JETC)* **2019**, *15*, 1–27. [CrossRef]

- 72. Odame, K.; Nyamukuru, M. Analog LSTM for Keyword Spotting. In Proceedings of the 2022 IEEE 4th International Conference on Artificial Intelligence Circuits and Systems (AICAS), Incheon, Republic of Korea, 13–15 June 2022; pp. 375–378. [CrossRef]

- Tsai, H.; Ambrogio, S.; Mackin, C.; Narayanan, P.; Shelby, R.M.; Rocki, K.; Chen, A.; Burr, G.W. Inference of Long-Short Term Memory networks at software-equivalent accuracy using 2.5M analog Phase Change Memory devices. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019; pp. T82–T83. [CrossRef]

- Adam, K.; Smagulova, K.; James, A.P. Memristive LSTM network hardware architecture for time-series predictive modeling problems. In Proceedings of the 2018 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Chengdu, China, 26–30 October 2018; pp. 459–462. [CrossRef]

- Li, F.; Chang, C.H.; Siek, L. A compact current mode neuron circuit with Gaussian taper learning capability. In Proceedings of the 2009 IEEE International Symposium on Circuits and Systems, Taipei, Taiwan, 24–27 May 2009; IEEE: Piscataway, NJ, USA, 2009; pp. 2129–2132.

- 76. Yang, M.; Yeh, C.H.; Zhou, Y.; Cerqueira, J.P.; Lazar, A.A.; Seok, M. A 1µW voice activity detector using analog feature extraction and digital deep neural network. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 11–15 February 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 346–348.

- 77. Ray, S.; Kinget, P.R. Ultra-Low-Power and Compact-Area Analog Audio Feature Extraction Based on Time-Mode Analog Filterbank Interpolation and Time-Mode Analog Rectification. *IEEE J. Solid State Circuits* **2022**, *58*, 1025–1036. [CrossRef]

- Sarkar, S.; Banerjee, S. An 8-bit low power DAC with re-used distributed binary cells architecture for reconfigurable transmitters. *Microelectron. J.* 2014, 45, 666–677. [CrossRef]

- 79. Kelly, B.M.; DiLello, A.T.; Graham, D.W. Reconfigurable analog preprocessing for efficient asynchronous analog-to-digital conversion. *J. Low Power Electron. Appl.* **2019**, *9*, 25. [CrossRef]

- 80. Cheng, C.H.; Yeh, F.S.; Chin, A. Low-power high-performance non-volatile memory on a flexible substrate with excellent endurance. *Adv. Mater.* **2011**, *23*, 902–905. [CrossRef]

- Miranda, E.; Suñé, J. Memristors for neuromorphic circuits and artificial intelligence applications. *Materials* 2020, 13, 938. [CrossRef]

- 82. Reynolds, D.A. Gaussian mixture models. Encycl. Biom. 2009, 741.

- 83. Alimisis, V.; Gennis, G.; Touloupas, K.; Dimas, C.; Uzunoglu, N.; Sotiriadis, P.P. Nanopower Integrated Gaussian Mixture Model Classifier for Epileptic Seizure Prediction. *Bioengineering* **2022**, *9*, 160. [CrossRef] [PubMed]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.